中国科大在硬件高斯随机数生成算法的研究中取得重要进展

近期,图书馆VIP在硬件高斯随机数生成算法的研究中取得重要进展,提出了一种新式的硬件高斯随机数生成器设计方法。该成果近日以“Flexible FPGA Gaussian Random Number Generators With Reconfigurable Variance”为题在线发表于电子工程领域知名期刊《IEEE Transactions on Circuits and Systems I: Regular Papers》。中国科大博士研究生陈卓为第一作者;中国科大宋克柱教授为通讯作者。

加性高斯白噪声(Additive white Gaussian noise, AWGN)模型通常被用来反映多种噪声共同作用的叠加结果,因此高斯随机数(Gaussian random number, GRN)生成器,作为一种能够生成加性高斯白噪声的硬件模块,是许多高性能硬件仿真系统中的重要部件,在通信系统仿真、金融仿真等场景下均有着重要作用。高斯随机数反映的是被仿真系统的随机性,而这一随机性通常是一些重要系统特征,例如SerDes系统中的误码,的形成原因。因此,高斯随机数生成器的统计学准确度会直接影响仿真结果的可靠性,高斯随机数生成器也是此类系统中的重要组成部件。

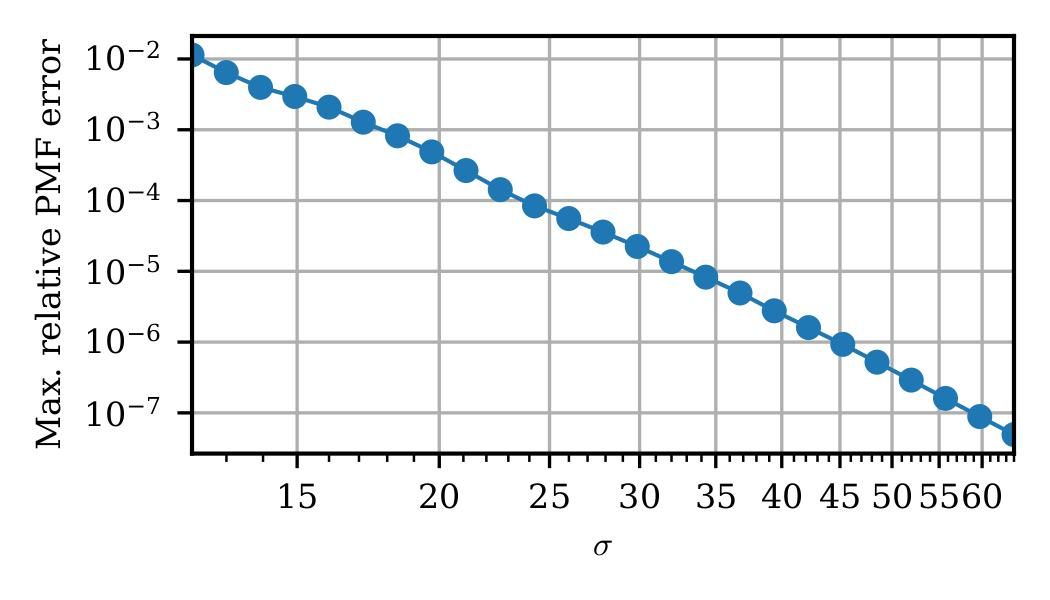

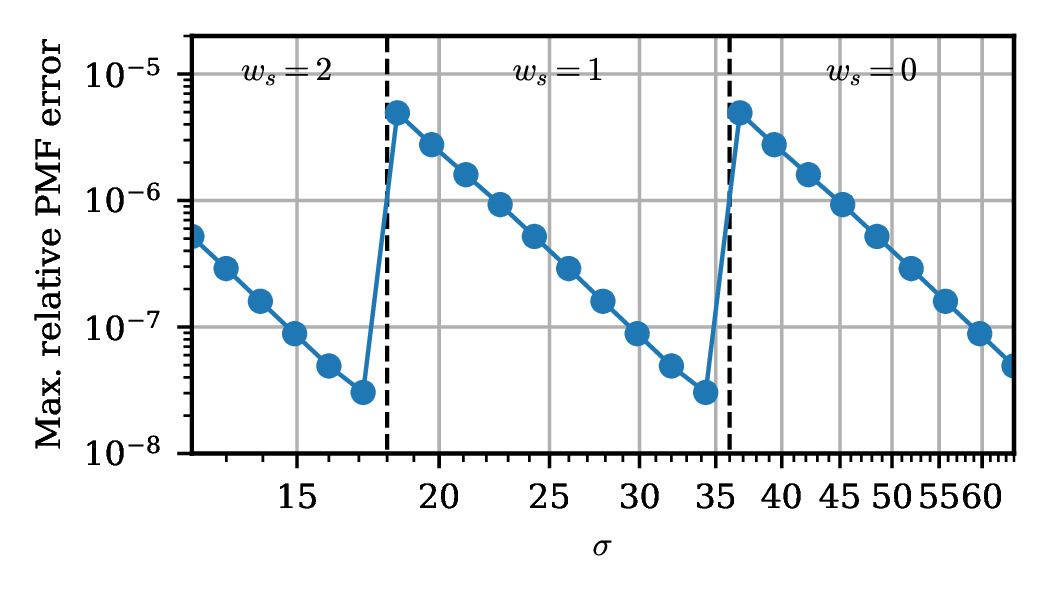

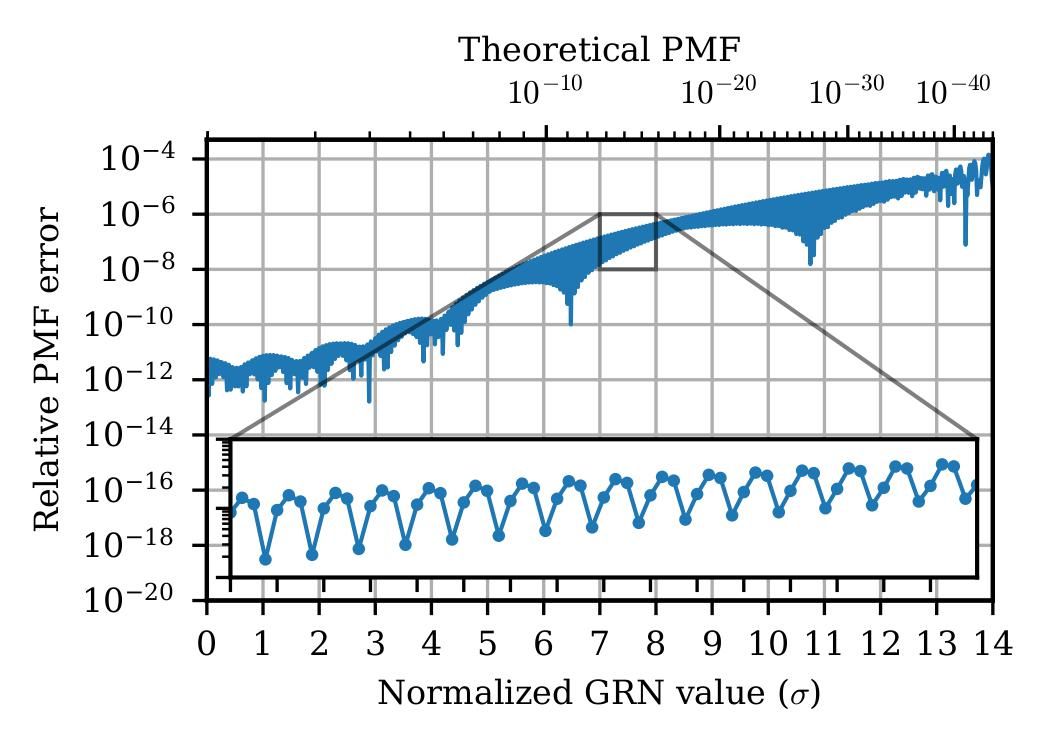

自从2000年工程师们尝试用硬件实现了Box-Muller算法后,关于硬件高斯随机数生成算法的研究就层出不穷。传统的适用于硬件的高斯随机数生成算法,包括Ziggurat法、Box-Muller法、Inversion法等,通常只针对σ=1的标准高斯分布,在硬件系统中使用时需要使用额外的乘法器和取整器,从而引入额外的硬件消耗和误差来源。此外,由传统方法设计的高斯随机数生成器的输出范围往往只能在参数设计完成后通过测试或理论分析得到,提高输出范围的方法不够直接。研究团队以一种相对较新的Piecewise-CLT算法作为基础,在对算法解析式的推导过程中,通过引入可变的σ值和预先确定的高斯随机数输出范围,获得了针对任意σ值和任意输出范围的高斯随机数生成器的设计方法,并以此设计出了理论输出范围达到±14σ的生成器(图1)。在尝试为算法引入可重配置性时,研究团队发现,如果直接重配置已有硬件架构的σ值,生成器的误差将随着σ值的降低而不断升高(图2),使其实用性大大降低。为了解决这一问题,该团队为算法引入名为缩放因子(scaling index)的参数,使得算法在针对不同σ值进行随机数生成时,会根据缩放因子的不同对相关数值进行缩放,从而得到相对稳定的误差曲线(图3),从而使得σ值的实时配置真正成为可能。

图 1 理论输出范围达到±14σ的生成器的相对概率误差与随机数大小的关系

图 2 未引入缩放因子时的误差曲线

图 3 引入缩放因子后的误差曲线

基于上述研究,研究团队提出了一种新式的硬件高斯随机数生成器设计方法。相较于传统的硬件高斯随机数生成器设计方法,该方法由于其支持任意σ值、任意输出范围、可重配置的优点,具有更大的灵活性和使用性,为设计高时钟速率、高并行度、高硬件资源利用率的高性能硬件仿真系统提供有力支持。

该项研究工作得到了国家重点研发计划项目的支持。

论文链接:https://ieeexplore.ieee.org/document/10477259

(物理学院、核探测与核电子学国家重点实验室、科研部)