中国科大在极低抖动高速锁相环芯片研究中取得重要进展

随着人工智能(AI)与6G时代的加速到来,超高速有线互联与毫米波无线互联技术变得日益重要。其中,极低抖动整数分频(Interger-N)与小数分频(Fractional-N)锁相环芯片扮演关键核心角色。

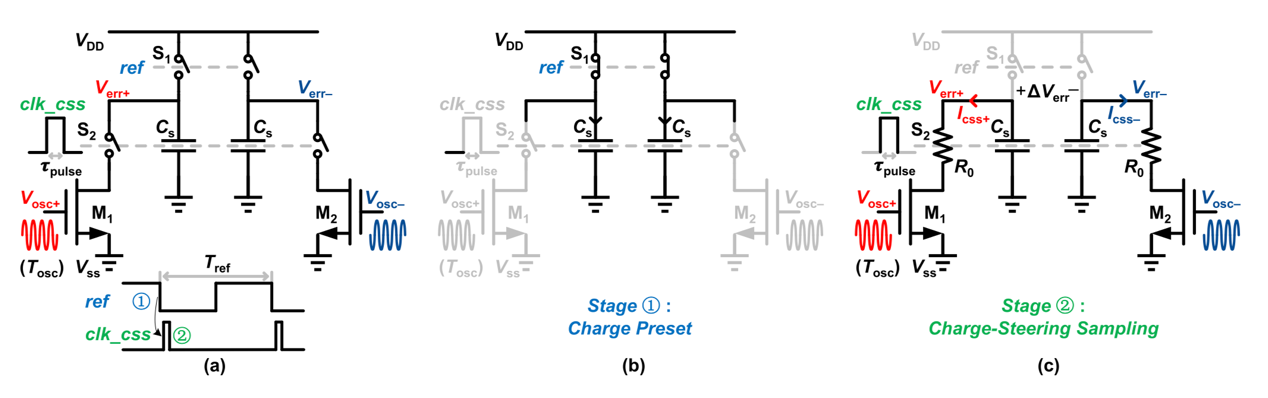

近日,我校微电子学院胡诣哲教授课题组在该领域研究取得重要突破,基于全新的“电荷舵采样技术”(Charge-Steering Sampling,见图1),分别提出了电荷域整数型和小数型高性能全数字锁相环架构,成功实现了最低约60飞秒(fs)抖动的性能。相关成果以《A PLL Technique: Charge-Steering Sampling》和《A Charge-Domain Fractional-NADPLL Based on Charge-Steering Sampling》为题,在集成电路领域著名期刊IEEE Journalof Solid-State Circuits(JSSC)连续发表,引发广泛关注。

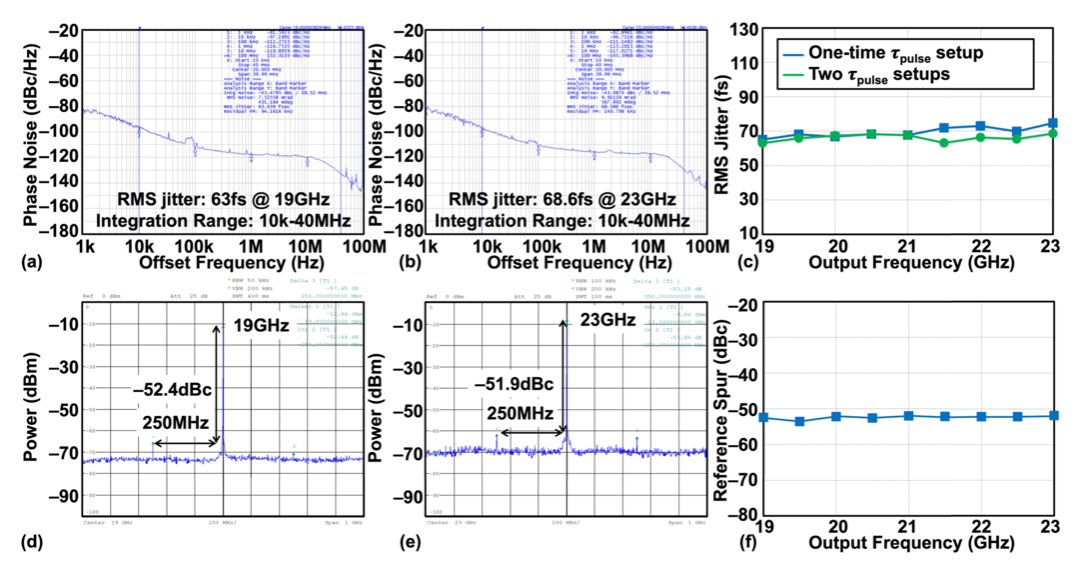

针对传统亚采样型模拟锁相环存在模拟滤波器面积大、采样隔离度低以及参考杂散显著等问题,论文《A PLL Technique: Charge-Steering Sampling》提出了一种基于“电荷舵采样”(Charge-Steering Sampling, CSS)机制的整数型全数字锁相环架构。该技术具备高相位检测增益,有效抑制带内量化噪声,并通过提升环路带宽进一步削弱数控振荡器(DCO)的相位噪声影响。同时,多bit数字相位输出显著提升了锁定速度与锁定鲁棒性。测试结果表明,该锁相环实现了63飞秒(fs)的时钟抖动和–52 dBc的参考杂散水平,具体性能如图2所示。

图1.提出的“电荷舵采样”技术工作原理

图2.基于“电荷舵采样”的整数型全数字锁相环测试结果

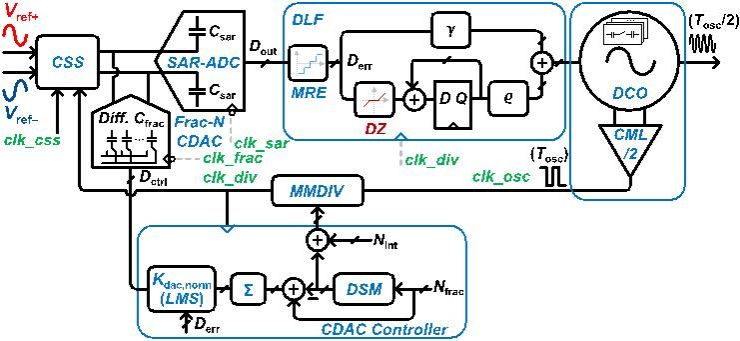

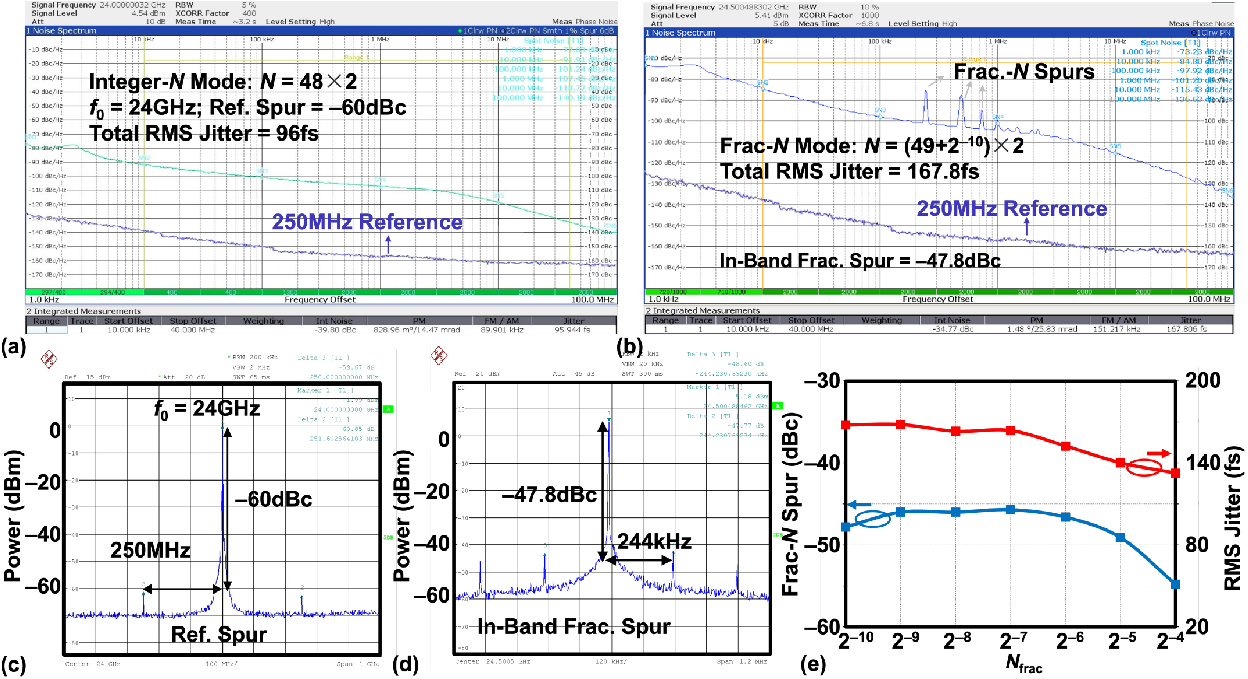

另一方面,传统基于数字时间转换器(DTC)的小数型锁相环,其抖动与小数杂散性能通常受限于DTC本身的相位噪声和非线性。为突破这一瓶颈,论文《A Charge-Domain Fractional-N ADPLL Based on Charge-Steering Sampling》提出了一种全新的电荷域小数型全数字锁相环架构(见图3)。该架构融合了三项关键技术:基于电荷舵采样(CSS)的高线性度相位检测、中升编码实现的高鉴相增益以及在电荷域内基于电容DAC的ΔΣ量化误差补偿机制,从而实现优异的小数分频性能。芯片测试频率范围为21–25 GHz,结果如图4所示:在整数模式下,积分抖动为96飞秒(fs),参考杂散达到–60 dBc;在小数模式下,积分抖动为168 fs,带内最差小数杂散为–48 dBc。

图3.电荷域小数型全数字锁相环架构

图4.电荷域小数型全数字锁相环测试结果

微电子学院博士生陶韦臣为上述两篇论文的第一作者,胡诣哲教授担任通讯作者。该研究工作得到了安徽省集成电路科学与技术重点实验室的大力支持。

论文链接:

1、https://ieeexplore.ieee.org/abstract/document/11017517。

2、https://ieeexplore.ieee.org/document/10981601。

(微电子学院、科研部)